V. Barashko, A. Korytov, <u>A. Madorsky</u>, G. Mitselmakher University of Florida/Physics

N. Bondar, V. Golovtsov, P. Levchenko, L. Uvarov, S. Vavilov, S. Volkov St. Petersburg Nuclear Physics Institute (PNPI)

## **GEM HV system main features**

#### Each voltage input powered from its own regulator

- Voltages are individually adjustable

- Voltages and Currents are measured on each channel

- **\***Over-, undervoltage, overcurrent protection on each channel

#### Complex chamber protection scenarios possible

- Example 1:

- □ Voltage difference between any two foils must not exceed X volts.

- Example 2:

- □ In case of overcurrent on a segment, first reduce the voltage by X volts, wait for Y seconds, if overcurrent does not disappear, reduce voltage by Z volts, etc.

#### GEM segment ganging will be needed to reduce channel count

# **Segment ganging options**

- In order to reduce HV output count, segments on segmented layers have to be ganged in groups

- Each group is powered from one HV output

- Each segment in a group powered via its own resistor

- Maximum segment capacitance requirement still followed

| Voltage (V)               | All foil<br>segments<br>unganged | Ganging<br>9 + 9 + 9 + 9 + 11 | Ganging<br>16 + 16 + 15 | All 47 foil<br>segments ganged<br>together<br>(baseline) |

|---------------------------|----------------------------------|-------------------------------|-------------------------|----------------------------------------------------------|

| -3760                     | 1                                | 1                             | 1                       | 1                                                        |

| -2860                     | 47                               | 5                             | 3                       | 1                                                        |

| -2410                     | 1                                | 1                             | 1                       | 1                                                        |

| -2060                     | 47                               | 5                             | 3                       | 1                                                        |

| -1620                     | 1                                | 1                             | 1                       | 1                                                        |

| -920                      | 47                               | 5                             | 3                       | 1                                                        |

| -500                      | 1                                | 1                             | 1                       | 1                                                        |

| HV Outputs per<br>chamber | 145 (not realistic)              | 19                            | 13                      | 7                                                        |

| HV Outputs in system      | 20880 (not<br>realistic)         | 2736                          | 1872                    | 1008                                                     |

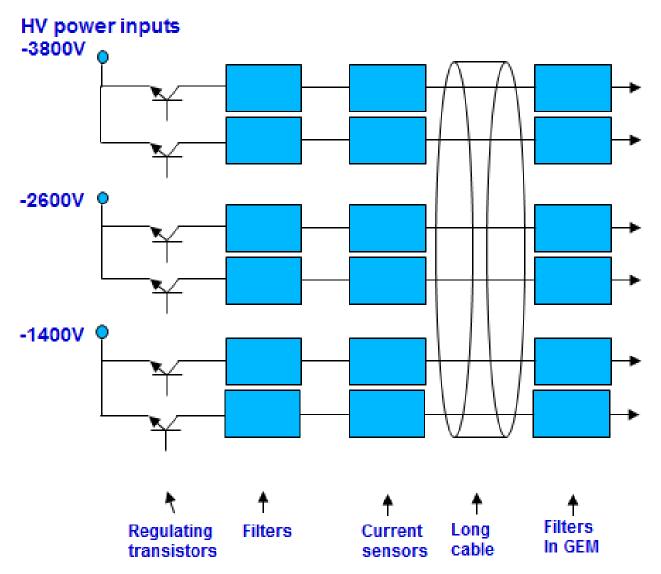

## **Block schematics**

- Build the following modules:

- One Distribution board

- One Master board

- Status:

- Distribution board: a few channels assembled and working

- Buying parts for one complete board now

- Master board:

- Buying parts now

- Based on existing design

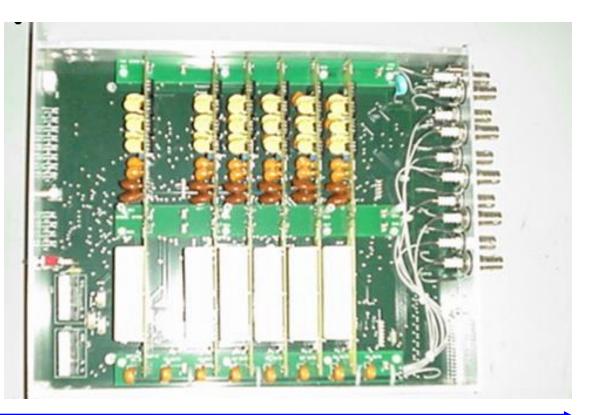

#### **Distribution board**

#### Master board (left)

Prototyping in PNPI is in good shape

**>**GEM should create a target specification for its HV system

Important:

- ➢ If UF/PNPI system is selected, then:

- **GEM** chamber design has to be adapted for UF/PNPI HV system

## **Necessary changes:**

- Because each segment group is powered from its own regulator:

- **Resistive divider should be removed**

- **Each group of segments should be connected to its own HV wire**

- **These wires should be attached to a multi-pin HV input connector**

- See table on page 2 for the HV pin count per chamber

# Test plan:

- Prototype will be ready in September-October 2014

- For a meaningful test, we'll need a chamber prototype designed as shown above

- UF can share the cost of such chamber prototype construction

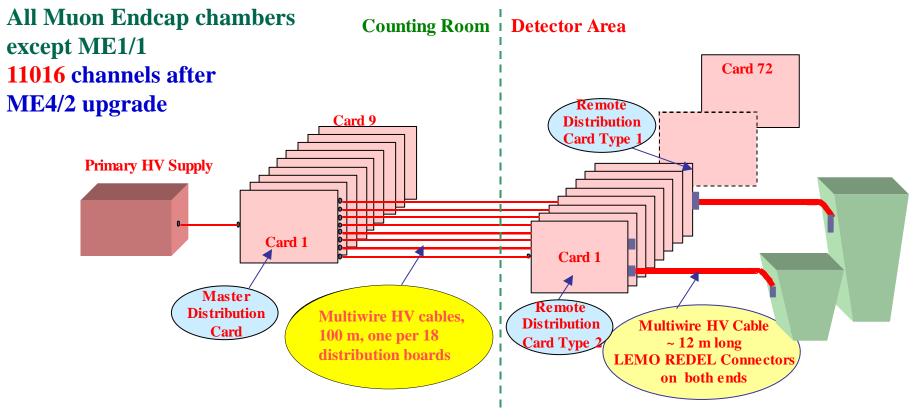

# **UF/PNPI HV system architecture**

#### •Primary HV power supplies: off the shelf

•Master board: One output per distribution board. Regulates voltage 0-4KV (VMAX), measures current on each output.

•Remote Distribution board: powers one large or two small chambers (36 outputs max). Regulates voltage 1KV down from VMAX, measures current on each output. Each output can be disconnected from HV if necessary.

UNIVERS

# **Primary HV Power supply**

- Off the shelf unit

- Matsusada AU type

- Up to 5KV output

- **≻ 60 mA**

- Control : RS-232

- > Overcurrent protection

- Door switch

- Floating output

## **Master board**

- CMS

- 8 channels

- Full range regulators 0-4KV

- Up to 1.5 mA per channel

- NOT rad-hard

- Located in S1 (control room)

- Voltage and current measurement on each channel

- Up to 38 channels

- Partial range regulators (~1KV down from input V)

- Each channel can be disconnected from load

- Remote-blow fuse

- Up to 100 uA per channel

- Rad-hard, magnetic field-tolerant

- Located in UXC (CMS cavern), near disks

- On each channel:

- Voltage and current limit programmable

- Voltage and current measurement

- Voltage resolution:

- **∻~1V**

- Current measurement resolution:

- **\*100 nA**

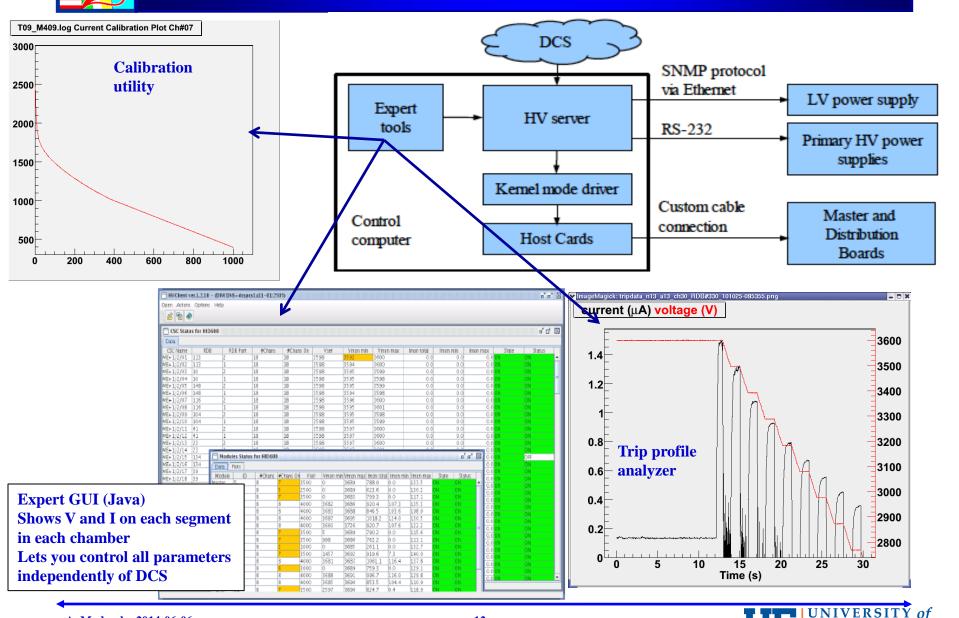

## **Software**

### **Purposes**

- Safety of the personnel

- Protection of the end-loads

- Protection of system components

## Fail-safe devices:

- Interlocks

- All long cables

- Primary HV PS overvoltage protection

- Remove PHVPS AC power in case of overvoltage

- Hardware watchdog

- Monitors main control software loop activity

- Turns PHVPS off if activity is missing for ~10 sec

### Protects against:

- □ software bugs

- Computer hardware failure

- Computer power cut-off

Overvoltage and overcurrent protection on each output channel

- All thresholds programmable

- Dead or disconnected board detection